Misją Instytutu jest dzialalność naukowo-badawcza prowadząca do nowych rozwiązań technicznych i organizacyjnych użytecznych w kształtowaniu warunków pracy zgodnych z zasadami bezpieczeństwa pracy i ergonomii oraz ustalanie podstaw naukowych do właściwego ukierunkowywania polityki społeczno-ekonomicznej państwa w tym zakresie.

Do wykonania tego modelu sygnalizatora ostrzegawczego w pojazdach uprzywilejowanych zintegrowanego z układem komunikacji niezbędny jest wybór odpowiedniej platformy sprzętowej, w szczególności mikrokontrolera lub procesora sygnałowego. W chwili obecnej na rynku elektronicznym istnieje znaczny wybór mikrokontrolerów i tanich procesorów sygnałowych, które mogły by znaleźć zastosowanie jako jednostka obliczeniowa w modelu sygnalizatora. Decydując o wyborze odpowiedniego typu układu brano pod uwagę wymaganą moc obliczeniową, dostępność oprogramowania i elementów peryferyjnych, dostępność wsparcia technicznego, perspektywy dalszego rozwoju platformy sprzętowej oraz koszt przyjętego rozwiązania (ze względu na przydatność społeczną i gospodarczą opracowywanego rozwiązania).

W pierwszej kolejności rozważano możliwość zastosowania w przyszłym modelu sygnalizatora jednego z szerokiej gamy dostępnych na rynku mikrokontrolerów. Są to niedrogie i powszechnie dostępne komponenty elektroniczne, często o znacznie rozbudowanej strukturze wewnętrznej. Tego typu procesory są stale i bardzo często unowocześniane a ich moc obliczeniowa stale wzrasta. W obecnej chwili niektóre rodzaje mikrokontrolerów (np. dsPIC) umożliwiają wykonywanie operacji zarezerwowanych dotychczas dla procesorów sygnałowych. Niemniej jednak przeprowadzona analiza parametrów dostępnych na rynku mikrokontrolerów pokazała, że implementacja algorytmów generatora sygnałów ostrzegawczych i jednocześnie kilku adaptacyjnych filtrów FIR będących podstawą działania układów aktywnej redukcji hałasu (docierającego do kierowcy oraz w torze komunikacji radiowej) może okazać się problematyczne nawet w przypadku najbardziej zaawansowanych z tych układów. W najlepszym przypadku zbyt mała moc obliczeniowa powodowała by konieczność ograniczania od góry częstotliwości przetwarzanych sygnałów lub zastosowania prostszych algorytmów adaptacji filtrów cyfrowych. Z tego powodu model sygnalizatora zintegrowanego postanowiono zbudować w oparciu o procesor sygnałowy.

Obecnie na świecie jest trzech liczących się producentów procesorów sygnałowych: Analog Devices, Freescale Semiconductors (dawniej Motorola) i Texas Instruments. W wyniku analizy możliwości oferowanych przez tych producentów procesorów sygnałowych ale również ich ceny, dostępności na rynku polskim, dostępu do dokumentacji, oprogramowania (asemblery, kompilatory) i wsparcia technicznego zdecydowano o wykorzystaniu procesorów Analog Devices, w szczególności ADSP-21364.

Procesor sygnałowy ADSP-21364 należy do rozwijanej od wielu lat przez Analog Devices linii procesorów określanych nazwą kodową SHARC. Jest on optymalizowany pod kątem zastosowań audio. Na Rys.1 pokazano schemat struktury wewnętrznej procesora.

Rys. 1. Schemat struktury wewnętrznej procesora ADSP-21364.

Do najważniejszych cech i parametrów tego procesora ADSP-21364 należą:

- częstotliwość zegara – 333MHz,

- liczba operacji zmiennoprzecinkowych – 2 GFLOPS (przy 333MHz),

- liczba operacji mnożenia i akumulacji – 666 MMACS (przy 333MHz),

- dwie jednostki arytmetyczno-logiczne (ALU) mogące operować na 32-bitowych liczbach stałoprzecinkowych oraz 32- i 40-bitowych liczbach zmiennoprzecinkowych,

- równoległe szyny danych i adresowe pozwalające wykonywać w jednym cyklu zegarowym kilku różnych operacji na danych i pamięci,

- 3Mbit wbudowanej pamięci SRAM,

- obsługa interfejsu testowego JTAG.

Tak duża moc obliczeniowa wyrażona liczbą operacji zmiennoprzecinkowych oraz operacji mnożenia i akumulacji w jednostce czasu powoduje, że procesor ten nie będzie miał żadnych problemów z realizacją algorytmów obliczeniowych przewidywanych dla modelu sygnalizatora zintegrowanego. Czas obliczeń dla filtru FIR jest wynosi 3ns/współczynnik. Zatem obliczenia dla filtru o długości 20 współczynników (przefiltrowanie kolejnej próbki sygnału) będzie trwało 60ns, przy czym procesor może wykonywać obliczenia dla dwóch filtrów równocześnie (dwie jednostki ALU).

Firma Analog Devices dla swoich procesorów sygnałowych udostępnia tzw. zestawy ewakuacyjne. Zestaw taki składa się z płytki ewaluacyjnej i odpowiedniego oprzyrządowania (zasilacze, kable, oprogramowanie, dokumentacja). Płytka ewaluacyjna zawiera docelowy procesor sygnałowy, wiele dodatkowych elementów peryferyjnych oraz interfejs do współpracy z komputerem. Dzięki temu zestaw ewaluacyjny umożliwia naukę programowania i obsługi wybranego procesora oraz opracowywanie i testowanie własnego oprogramowania.

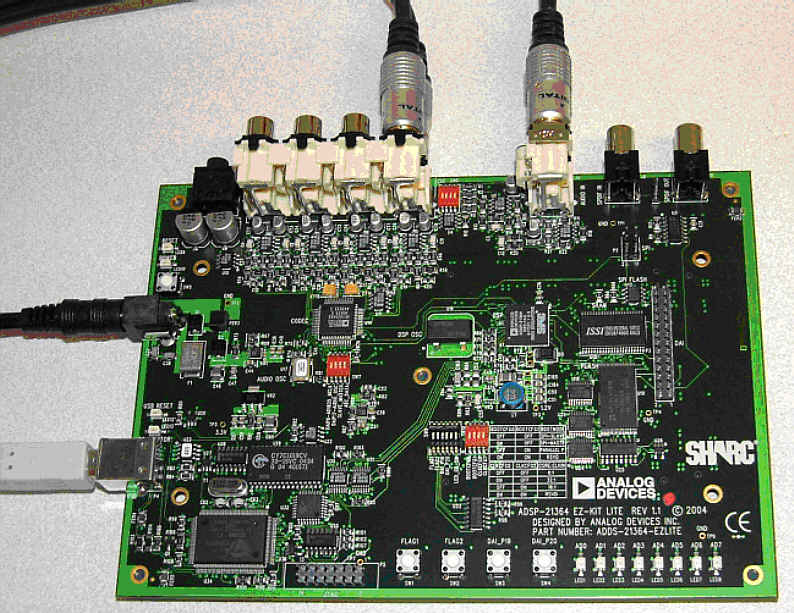

Na Rys.2 pokazano wygląd zakupionej na potrzeby realizacji zadania płytki ewaluacyjnej procesora ADSP-21364 a na Rys.3 jej schemat blokowy.

Rys. 2. Płytka ewaluacyjna procesora sygnałowego SHARC ADSP-21364.

Rys. 3. Schemat blokowy płytki ewaluacyjnej procesora sygnałowego ADSP-21364.

Płytka ewaluacyjna obok procesora sygnałowego zawiera m.in.:

- układy zasilania,

- złącze USB i interfejs USB-JTAG do współpracy z komputerem,

- złącze JTAG,

- pamięci: SRAM (512K x 8bit), Flash (1M x 8bit) i SPI (512Kb),

- kodek (zespół przetworników A/C i C/A) audio pracujący z częstotliwościami próbkowania do 96kHz,

- cztery stereofoniczne liniowe wyjścia audio (złącza RCA),

- jedno stereofoniczne liniowe wejście audio (złącza RCA) z możliwością podłączania wkładek mikrofonów elektretowych (zasilanie wkładki i większe wzmocnienie),

- stereofoniczne wyjście słuchawkowe (ze wzmacniaczem),

- wejście i wyjście cyfrowego sygnału audio typu S/PDIF,

- diody LED ogólnego przeznaczenia (do wykorzystania we własnych aplikacjach),

- przyciski ogólnego przeznaczenia (do wykorzystania we własnych aplikacjach).

Rozbudowane układy peryferyjne umieszczone na płytce ewaluacyjnej pozwalają na wykorzystanie jej do uruchamiania i testowania bardzo szerokiej gamy programów do cyfrowego przetwarzania sygnałów audio, w tym oprogramowania realizującego sygnalizator akustyczny zintegrowany z układem komunikacji i układem aktywnej redukcji hałasu.

Ważnym elementem zestawu ewaluacyjnego jak i elementem platformy sprzętowej są różnego rodzaju programy komputerowe i ich elementy wspomagające tworzenie oprogramowania dla procesora sygnałowego. Należą do nich m.in.:

- edytor i kompilator programów pisanych w języku wysokiego poziomu - C++ (Visual DSP),

- edytor i kompilator programów pisanych w asemblerze procesora,

- debugger,

- linker,

- program ładujący,

- biblioteki gotowych funkcji i procedur.

Duże możliwości oraz wszechstronność zarówno samego procesora sygnałowego jak i układu ewaluacyjnego niosą jednak ze sobą pewne niedogodności - podstawowa dokumentacja procesora i jego oprogramowania, z którą należy się zapoznać aby rozpocząć pracę z procesorem i w dostatecznym stopniu wykorzystać jego możliwości liczy ponad 10 tys. stron tekstu.